Performance Analysis of a Per-Row Activation Counting Mechanism in DRAM

Abstract

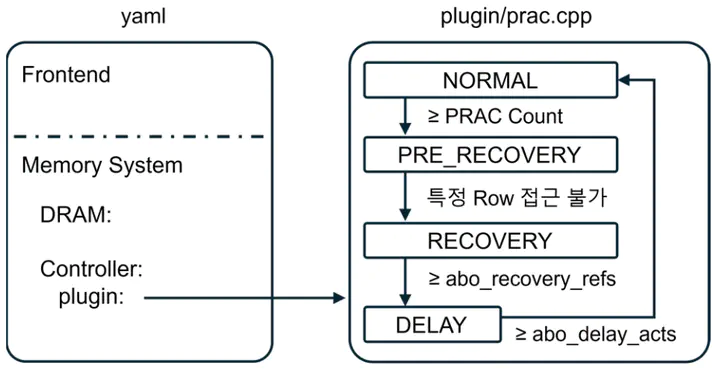

In this study we evaluate the performance overhead of per-row activation counting (PRAC) mechanism employed in DDR5 DRAM. PRAC is designed to handle the security attacks against DRAM cells by enabling refresh to target and adjacent rows based on access counts since the last activation. However, PRAC requires additional peripheral circuits that increase DRAM timing and refresh counts, thus PRAC may provoke significant performance overhead. In order to investigate the performance hurdles by PRAC in DRAM, we analyze the performance impacts by adjusting DRAM timing parameters and refresh controls when PRAC is enabled in DRAM. We use the cycle-accurate DRAM simulator to evaluate the performance changes by various PRAC configurations. Our evaluation exhibits the performance overhead by PRAC is 8.5% on average when PRAC configurations are set up based on the JEDEC DDR5 standard.